中国首颗自主研发DRAM芯片年底量产,长鑫存储传拟扩产一倍应战

嘉宾专访 2019-10-08 18:17 DeepTech深科技

2019 年是中国“存储元年”,在长江存储 64 层 3D NAND 芯片宣布量产后,成功填补国内闪存技术的空白。另一家专攻 DRAM 的存储大厂合肥长鑫也将在年底生产首颗 8Gb DDR4 芯片,将会是中国第一颗自主研发的 DRAM 内存芯片。

国内存储技术无论是 NAND Flash 或 DRAM 都是从零开始研发,努力了 3 ~ 4 年后,陆续打破零自制的现状,是一个很重要开始。

合肥长鑫成立于 2016 年,以 14 个月的速度完成 12 寸晶圆厂房,年中已完成 1.5 万片的测试晶圆,目前 19nm 工艺技术的良率如期且顺利,非常有机会在年底开始生产 8Gb DDR4 芯片,第一个应用领域会是计算机。

长鑫已经准备 2 万片产能应战,待年底试产成功后要启动大量生产。

同时,业界也传出长鑫存储对于目前技术非常有信心,考虑扩增一倍月产能规模至 4 万片,让机台设备的采购能一次到位,进入规模战的第一个门槛。

DRAM技术来源神秘面纱卸下

自从长鑫存储 CEO 朱一明在今年 5 月 GSA 存储论坛中揭露 DRAM 技术研发的种子是来自于过去曾经叱咤一时的欧系存储大厂奇梦达(Qimonda)后,长鑫存储也逐渐卸下神秘面纱,逐一揭露更多 DRAM 研发的细节与成果,一方面是要大家分享国产自主研发 DRAM 技术的重大成果,另一方面也有向客户宣传的意味。

在深圳登场的 NAND Flash 产业年度大会中国闪存市场峰会 CFMS 上,长鑫存储的未来技术评估实验室副总裁平尔萱也揭露了更多 DRAM 技术制程的细节,主要分为两大方向:

过去两大技术林立,DRAM 主流是如何走到堆叠式架构?

逻辑制程已经走到 7nm、5nm,DRAM 技术有能力走到 10nm 以下吗?

两大DRAM技术:堆叠、沟槽之争

DRAM 技术其实比 3D NAND 难很多,与逻辑制程相较,最大的不同是 DRAM 有一个电容,而这个电容的制成需要经过高温的步骤,因此,不太能用传统的晶体管制成 DRAM ,这也是当中技术的关键所在。

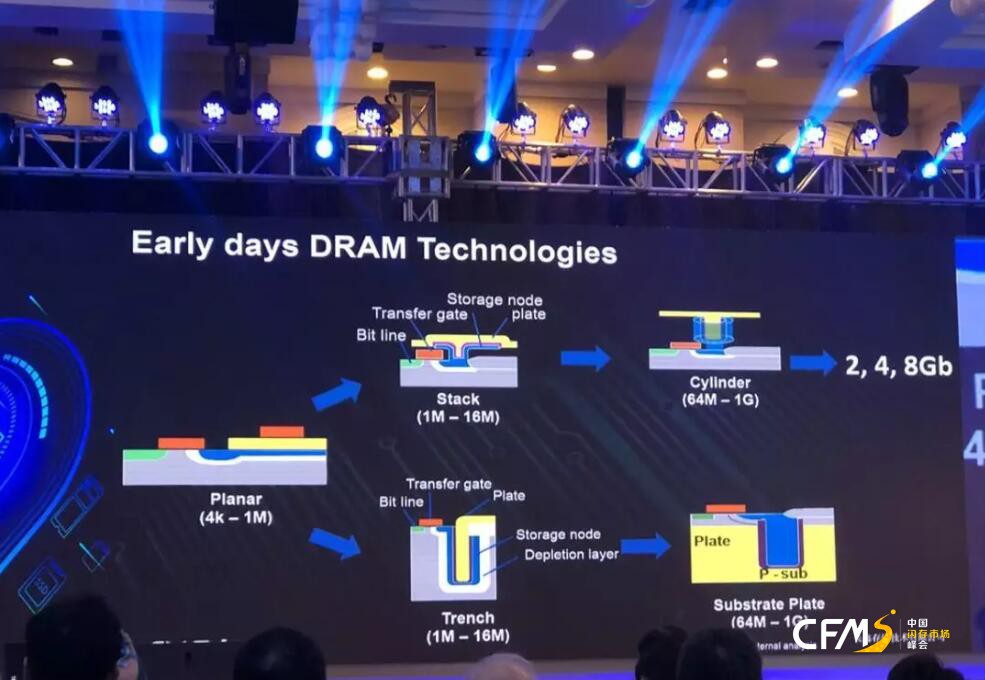

平尔萱从 DRAM 技术近 50 年的发展史来解释。他表示,DRAM 是在 60 年代发明出来,在 70 年代开始进入市场,经历这 50 年来有几波重大改变,像是从早期的平面结构演变成各种不同的结构。

最早期的 DRAM 是平面式的架构,随着 DRAM 线宽的减少导致表面积缩减,电容值已经无法满足,因此 DRAM 架构演变成两种,向上堆叠或是向下挖的沟槽式技术,以空间结构争取更多的表面积。

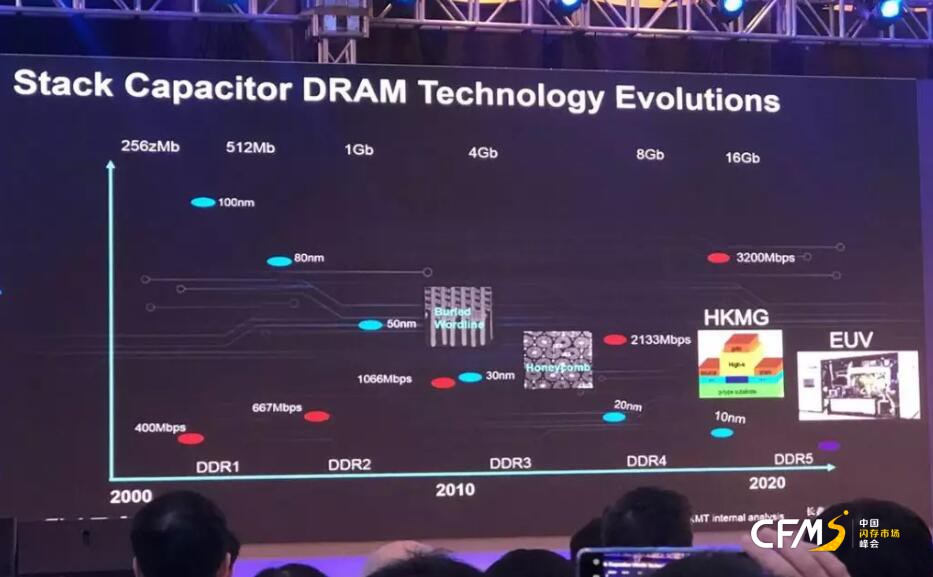

堆叠式技术和沟槽式技术在并存近 30 年后,后者随着奇梦达结束,DRAM 主流确定是堆叠式技术。

相较于沟槽式技术,堆叠式技术的优势是因为可以用内表面、外表面这两面作为电容,在同样的高度下,电容值可以做到比下面多一倍。随着 IC 的线宽逐渐的见效,下面堆叠式的就可以在小的面积里制造出大的电容值,这是因为线宽减少后,基于面积考虑上衍伸出来的一个技术优势。

从 2008 年开始,全球 DRAM 技术架构就开始从沟槽式转至堆叠式的技术研发。

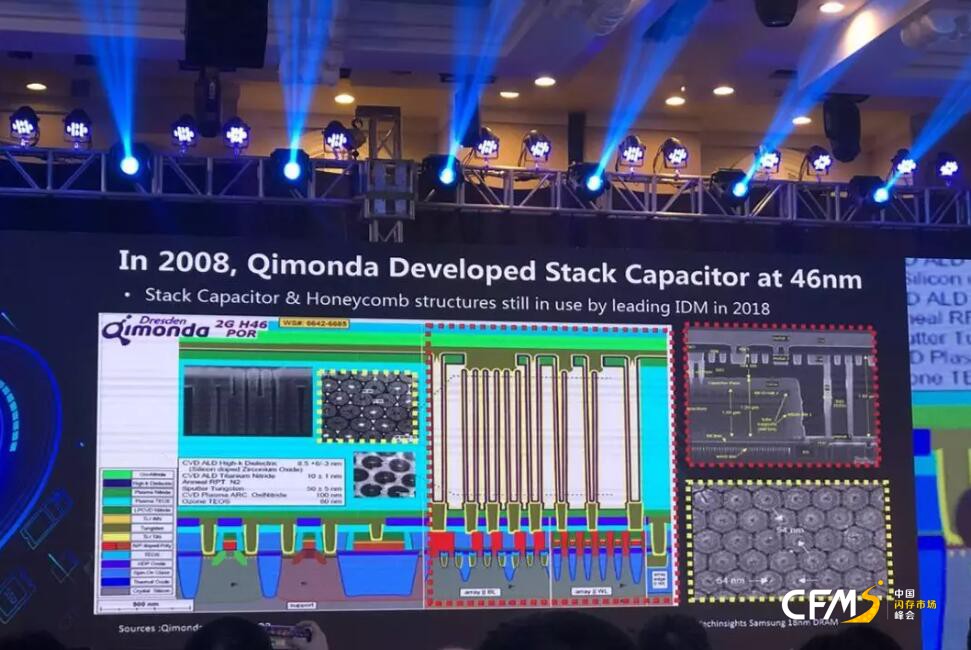

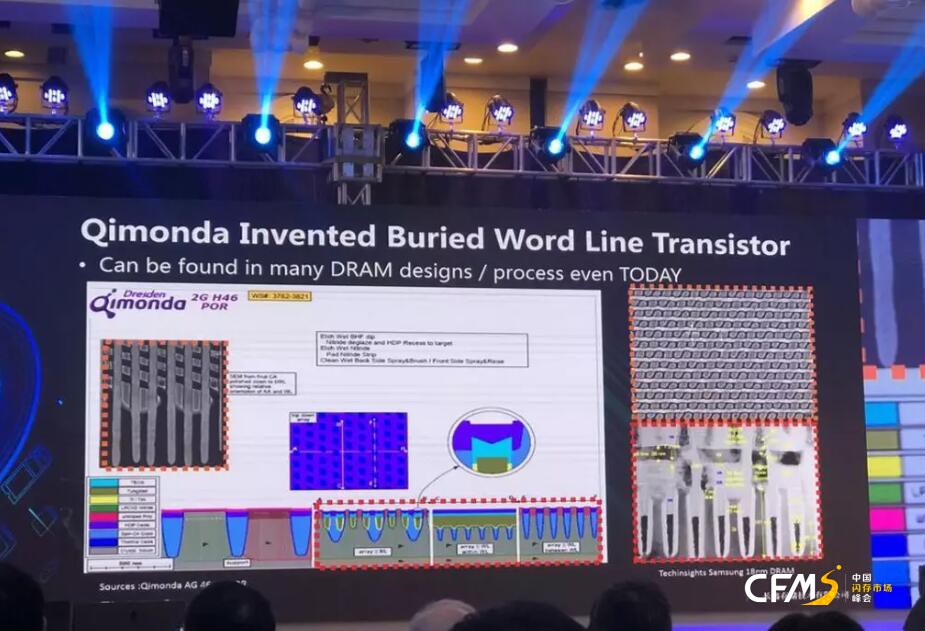

奇梦达在 2009 年宣布破产之前,其实已经成功研发堆叠式 DRAM 技术 Buried Wordline,46nm 工艺的产品已经在实验室中证实是可行的,且与上一代 58nm 工艺相比,晶圆数量增加 100% ,只可惜奇梦达成功研发出堆叠式 DRAM 技术,但当时 DRAM 市况恶化,已经无法取得资金让该技术进入生产了。

平尔萱博士也分析,奇梦达 Buried Wordline 技术其实也些不错的贡献一直被沿用,例如采用了内外两面的电容增大面积。另外,采用更加紧密的排列,让单位面积中电容可以达到最大值。

还有一个重要概念是,怎么样将让线宽不断微缩的晶体管性能更好?再者,他们也发明将晶体管做在表面下面,可在逐渐减少的面积中利用空间提高晶体管的性能。

回顾堆叠式 DRAM 历史,排布的电容是在 30nm 工艺开始逐渐广泛使用,再微缩进入成 20nm 的 DRAM 工艺技术,然后在这之后需要做许多改变包括要引入晶体管使得外围线路的功能增加等。

再者,将光刻机入极紫外光 EUV 技术导入,也是让微缩延续的方式之一,使得 DRAM 的信号得到加强。

他表示,DRAM 技术一直在往前进,从双重图案对准(SADP)走向四重图案对准(SAQP)技术,还有,从内外双面电容逐渐走到外部的单面积电容,也就是柱状电容。

此外,逻辑制程已经走到 7nm 和 5nm 工艺技术,DRAM 工艺技术也要往下走到 10nm 以下,开发环绕式三节晶体管结构 GAA(Gate-all-around),还有开发新型的存储器技术等,整个来看,未来存储技术还有很多新的变局和成果延伸。

除了合肥长鑫存储的 DRAM 进展顺利,预计年底量产外,紫光集团日前也成立 DRAM 事业部,由集团执行副总裁高启全策划,同样预计进军 DRAM 技术自主开发和生产。

业界认为,长江存储的 3D NAND 开发成功,从 32 层到今日量产 64 层技术,2020 年迈入 128 层,一步步缩小与国际大厂之间距离,未来转到 DRAM 技术研发上,仍是不小的挑战。

紫光的 DRAM 技术火苗是西安紫光国芯,过去是奇梦达在西安的研发中心,目前这个设计研发团队约有 400~500 人左右。

中国半导体在存储产业的发展上虽然较晚,但不到五年的时间陆续有好消息问世,一一终结存储芯片“零”自制现况,有后发先至的好发展,但芯片量产后,仍是要过国际大厂的专利检视这一关,也将会是一大挑战。